数字微反射镜 DMD 数字微镜器件

数字微反射镜 DMD 数字微镜器件

数字微镜器件(Digital Micromirror Device,DMD)

是光开关的一种,利用旋转反射镜实现光开关的开合,开闭时间稍长,为微秒量级。作用过程十分简单,光从光纤中出来,射向DMD的反射镜片,DMD打开的时候,光可经过对称光路进入到另一端光纤;当DMD关闭的时候,即DMD的反射镜产生一个小的旋转,光经过反射后,无法进入对称的另一端,也就达到了光开关关闭的效果。

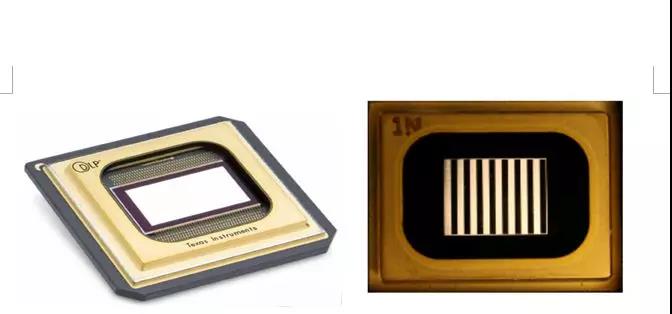

DMD(数字微镜器件)是一种由多个高速数字式光反射开光组成的阵列。DMD是由许多小型铝制反射镜面构成的,镜片的多少由显示分辨率决定,一个小镜片对应一个像素。相对于TFT-LCD(液晶)的透射率低,对比度小,DMD的反射率高,对比度大。将物体成像于DMD器件上,通过DMD器件的像素级可控特性及其高速的翻转频率,再将每个像点依次扫描到探测器上,实现白天对可见光条件下物体的高速被动式点扫描成像。加入适当光源还可实现主动式扫描成像。

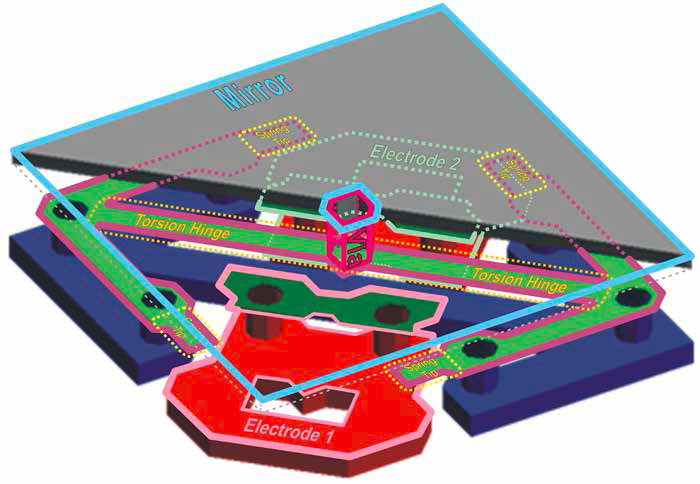

DLP产品采用的DLP技术原理简介:每一个 DLP 芯片组的核心都有一个高反射铝微镜阵列,即数字微镜器件 (DMD)。DMD 是一种电子输入、光学输出的微机电系统 (MEMS),开发人员可借助该系统执行高速、高效及可靠的空间光调制。采用 TI 成熟的半导体生产技术,每一个 DMD 都含有最多 200 万个独立控制的微镜(构建于相应的 CMOS 存储单元上)。在运行期间,DMD 控制器为每个基本存储单元加载一个“1”或一个“0”。接下来会施加镜像复位脉冲,这会引起每个微镜静电偏离大约一个铰链,从而达到相应的 +/-12° 状态。由于会受到两个弹簧顶针的阻力而物理停止,这两个有效状态的偏离角度是可重复的。在投影系统中,+12° 状态对应“开”像素,-12° 状态对应“关”像素。通过对每个镜片的开/关占空比进行编程来创建灰度图形,并且可以多路复用多个光源以创建 RGB 全彩图像。

数字微镜器件是光开关的一种,利用旋转反射镜实现光开关的开合。Digital Micromirror Device,DMD是光开关的一种,利用旋转反射镜实现光开关的开合,开闭时间稍长,为微秒量级。作用过程十分简单,光从光纤中出来,射向DMD的反射镜片,DMD打开的时候,光可经过对称光路进入到另一端光纤;当DMD关闭的时候,即DMD的反射镜产生一个小的旋转,光经过反射后,无法进入对称的另一端,也就达到了光开关关闭的效果。

DLP技术应用广泛,包括医疗成像、光纤网络、生命科学、光谱分析、光学测量和无掩模光刻。还有,共焦距显微技术,全息数据存贮,结构照明,立体显示等。

DMD数字微镜

DLP技术原理简介:每一个 DLP 芯片组的核心都有一个高反射铝微镜阵列,即数字微镜器件 (DMD)。DMD 是一种电子输入、光学输出的微机电系统 (MEMS),开发人员可借助该系统执行高速、高效及可靠的空间光调制。采用 TI 成熟的半导体生产技术,每一个 DMD 都含有最多 200 万个独立控制的微镜(构建于相应的 CMOS 存储单元上)。在运行期间,DMD 控制器为每个基本存储单元加载一个“1”或一个“0”。接下来会施加镜像复位脉冲,这会引起每个微镜静电偏离大约一个铰链,从而达到相应的 +/-12° 状态。由于会受到两个弹簧顶针的阻力而物理停止,这两个有效状态的偏离角度是可重复的。在投影系统中,+12° 状态对应“开”像素,-12° 状态对应“关”像素。通过对每个镜片的开/关占空比进行编程来创建灰度图形,并且可以多路复用多个光源以创建 RGB 全彩图像。

D4100 Key Specifications | |||||||

DMD Format | 0.7″ XGA | 0.95″ 1080P | 0.96″ WUXGA | ||||

Wavelength |

|

| VIS | ||||

DMD Package | Type A | Type A | Type A | ||||

DMD Interface | 2 x LVDS | 2 x LVDS | 2 x LVDS | ||||

Mirror Blocks | 16 | 16 | 16 | ||||

Mirror Pitch | 13.68 um | 10.8 um | 10.8 um | ||||

Reset and Settle Time | 13.4 us (est) | 13.4 us (est) | 13.4 us (est) | ||||

Clock Rate | 400 MHz DDR | 400 MHz DDR | 400 MHz DDR | ||||

Data Lines | 32 LVDS pairs | 64 LVDS pairs | 64 LVDS pairs | ||||

Data Transfer | 25.6 Gbs | 51.2 Gbs | 51.2 Gbs | ||||

Pattern Rates (binary/8-bit) | 22,727Hz/290hz | 10,638Hz/250Hz | 10,638Hz/250Hz | ||||

Row Address | Sequential Shift Register, Random Access, Single Line, & Global/Full Array | ||||||

Controller | Xilinx Virtex 5 LX50 Application FPGA, USB 2.0, SODIMM (up to 4GB DDR2 SDRAM) | ||||||

Features | Power Supply, Dual 120-pin EXP connectors, Mictor & JTAG Test/Debug Headers, Cypress 68013 USB Controller, SPI Flash, Remote DMD Board w/ Flex Cable | ||||||